因PCB高速問題而產生的信號過沖、下沖、反射、振鈴、串擾等,系統正常時序受嚴重影響,系統時序余量的減少迫使人們關注影響數字波形時序和質量的各種現象。由于速度的提高使時序變得更苛刻,無論對系統原理多么熟悉,任何忽略和簡化都可能給系統帶來不良影響。在PCB高速設計中時序問題是至關重要的,本文將著重討論高速設計中時序分析及仿真策略。

公共時鐘同步的時序分析及仿真

在高速數字電路中,數據的傳輸一般都通過時鐘對數據信號進行有序的收發控制。芯片只能按規定的時序發送和接收數據,過長的信號延遲或信號延時匹配不當都可能導致信號時序的違背和功能混亂。在低速系統中,互連延遲和振鈴等現象都可忽略不計,因為在這種低速系統中信號有足夠的時間達到穩定狀態。但在高速系統中,邊沿速率加快、系統時鐘速率上升,信號在器件之間的傳輸時間以及同步準備時間都縮短,傳輸線上的等效電容、電感也會對信號的數字轉換產生延遲和畸變,再加上信號延時不匹配等因素,都會影響芯片的建立和保持時間,導致芯片無法正確收發數據、系統無法正常工作。

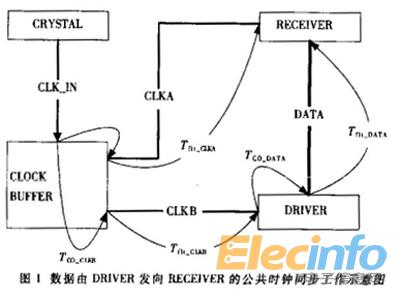

所謂公共時鐘同步,是指在數據的傳輸過程中,總線上的驅動端和接收端共享同一個時鐘源,在同一個時鐘緩沖器(CLOCK BUFFER)發出同相時鐘的作用下,完成數據的發送和接收。圖1所示為一個典型的公共時鐘同步數據收發工作示意圖。圖1中,晶振CRYSTAL產生輸出信號CLK_IN到達時鐘分配器CLOCK BUFFER,經CLOCK BUFFER分配緩沖后發出兩路同相時鐘,一路是CLKB,用于DRIVER的數據輸出;另一路是CLKA,用于采樣鎖存由DRIVER發往RECEIVER的數據。時鐘CLKB經Tflt_CLKB一段飛行時間(FLIGHT TIME)后到達DRIVER,DRIVER內部數據由CLKB鎖存經過TCO_DATA時間后出現在DRIVER的輸出端口上,輸出的數據然后再經過一段飛行時間Tflt_DATA到達RECEIVER的輸入端口;在RECEIVER的輸入端口上,利用CLOCK BUFFER產生的另一個時鐘CLKA(經過的延時就是CLKA時鐘飛行時間,即Tflt_CLKA)采樣鎖存這批來自DRIVER的數據,從而完成COMMON CLOCK一個時鐘周期的數據傳送過程。

以上過程表明,到達RECEIVER的數據是利用時鐘下一個周期的上升沿采樣的,據此可得到數據傳送所應滿足的兩個必要條件:①RECEIVER輸入端的數據一般都有所要求的建立時間Tsetup,它表示數據有效必須先于時鐘有效的最小時間值,數據信號到達輸入端的時間應該足夠早于時鐘信號,由此可得出建立時間所滿足的不等式;②為了成功地將數據鎖存到器件內部,數據信號必須在接收芯片的輸入端保持足夠長時間有效以確保信號正確無誤地被時鐘采樣鎖存,這段時間稱為保持時間,CLKA的延時必須小于數據的無效時間(INVALID),由此可得出保持時間所滿足的不等式。