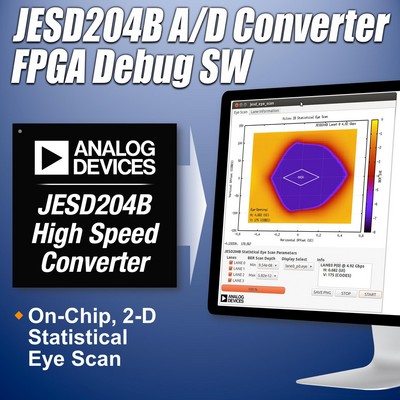

Analog Devices, Inc. 全球領先的高性能信號處理解決方案供應商,今天發布了一款基于FPGA的參考設計及配套軟件和HDL代碼,該參考設計可降低集成JESD204B兼容轉換器的高速系統的設計風險。該軟件為JESD204B Xilinx收發器調試工具,可支持312.5Mbps至12.5Gbps的 JESD204B數據轉換器 至FPGA串行數據接口和Xilinx? Inc., 7系列FPGA及Zynq?-7000全可編程SoC。它隨ADI轉換器免費提供,通過提供片內二維統計眼圖掃描,幫助雷達陣列、軟件定義無線電以及其他高速系統的設計人員更快地驗證采用千兆收發器的JESD204B數據轉換器至FPGA設計的信號完整性。

JESD204B FPGA調試軟件加快高速設計速度

Xilinx高速I/O產品經理Revathi Narayanan表示:“ADI的JESD204B Xilinx收發器調試工具提供了片內眼圖掃描功能,能以統計手段確定FPGA內部信號的完整性,是測試和測量流程的有效補充。其他技術均針對FPGA封裝的外部,并在Xilinx自動增益控制和均衡器模塊處理之前采集信號,而ADI則利用Xilinx收發器片內眼圖掃描功能,使開發人員可以監控FPGA內部JESD204B鏈路上的信號完整性和設計裕量,從而獲得更加準確的結果。”

ADI的參考設計直接從7系列IBERT內核中的片內Rx裕量分析功能收集數據,并在FPGA或者ARM?雙核Cortex?-A9 MPCore?處理器之一的內部管理本地數據,在HDMI顯示器上顯示數據,或者通過以太網將數據送至遠程監控站。一般地,其他掃描工具在片外測量信號,需要使用昂貴的測試和測量設備,或者需要通過JTAG傳回數據,以便在實驗室的主機/開發電腦上查看。

“實時”數據采集功能可監控設備健康狀態

替代型掃描工具一般通過生成偽隨機位流(PRBS)的方式來測量高速數據鏈路,而系統會在封閉開發環境中校驗該偽隨機位流的位級正確性。這種方式并不描述設計的實際表現,也不說明設計是否可能瀕臨失敗。ADI的參考設計使用流向FPGA的真實JESD204B串行數據來測量鏈路的穩健性。通過這種利用“實時”數據的方式,即使已在現場部署設計之后,也可監控信號的保真度,從而在產品的壽命周期內進行實時、預見性維護。

報價與供貨